Project Description

The DI-ReDesign project focuses on advancing design automation for reconfigurable field-effect transistors (RFETs). RFETs can be electrically configured to operate as either an n-type or a p-type transistor. This property enables greater flexibility, compactness, and efficiency in logic design of current electronic design automation (EDA) flows.

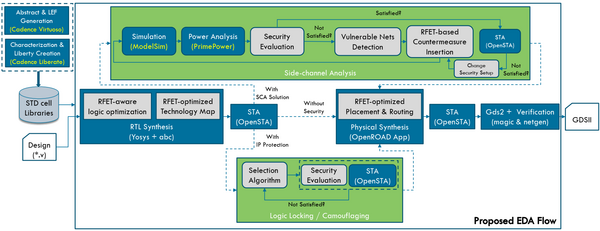

The first component of the project is the development of an open-source RFET standard cell library to capture functional, timing, and layout characteristics. These cells are designed and validated through formal methods, SPICE simulations, and ultimately silicon measurements. Their integration into the Open-Source tool flow will extend conventional digital flows to account for RFET-specific features such as polymorphism and self-duality, ensuring optimized synthesis and placement while maintaining compatibility with established CMOS-based methodologies.

The second component of the project is to integrate of hardware security into the design and synthesis flow. The project aims to input protective measures directly into synthesis and placement rather than treating them as post-design additions. This includes layout strategies to mitigate side-channel leakage, as well as logic camouflaging and locking techniques to protect against reverse engineering and intellectual property theft. Furthermore, the flow incorporates evaluation tools to assess circuit resilience against advanced adversaries, including machine learning-based attacks, and uses these assessments to guide iterative improvements.

The expected outcome is an open, accessible EDA (Figure 1) framework and RFET cell library that not only enables practical design with emerging devices but also yields secure digital circuits. This approach supports both technological innovation and resilience, contributing to a sustainable semiconductor ecosystem.

Papers

- Flip-UnLock: An Anomaly Detection Attack on Flip-Flop-Based Logic Locking. (ISVLSI)

- Flip-Break: A GNN-Based Attack on Flip-Flop Logic Locking

- RAT: RFET-Based Analog Hardware Trojan. (ISVLSI)

- Verilog-A look-up table model of a TIG-RFET compatible with 22nm FDSOI design rules Satisfying Gummel Symmetry. (MOCAST)