Project Description

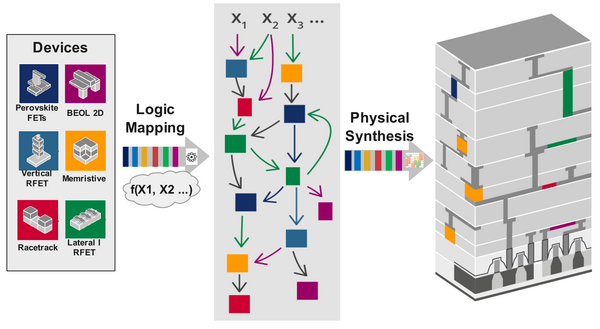

The TRR404 "Next Generation Electronics With Active Devices in Three Dimensions [Active-3D]" proposes to design novel 3D architectures with emerging technologies for logic, memory, and routing. These novel components in all three domains will bring in new hitherto unseen functionalities. Many of these components are expected to bring in reconfigurable features where a component can function as both a logic and memory device, or another that can compute and route signals. Such components blur the distinction between the traditional logic, memory, and routing. This project aims to design novel algorithms to design efficient circuits by exploiting the benefits brought in by the novel devices being developed in Active-3D, as shown in Figure 1. The work in this project is primarily divided into two parts: logic mapping and physical synthesis. Logic mapping refers to transforming a target application's functional description into a network of standard cells. The work for logic mapping in this project will focus on analyzing the precise features of the novel devices for their applicability and impact on EDA algorithms. We will then study how these features can be represented in the design libraries. Novel logic mapping algorithms will need to be developed to exploit these properties. Physical synthesis is about translating the standard cell network into a layout that can eventually be taped out. Since we are dealing with a novel Active Back-End of Line (ABEOL) in this project, the physical synthesis algorithms need to be redesigned since the target implementation architecture is completely different from what the traditional EDA tools and algorithms are capable of handling. A 3D architecture template will also be designed, which is capable of handling the novel features of the devices and enabling the connections in the third dimension.

Employees Responsible

Citations

- Kavand, Nima, et al. "RAT: RFET-based Analog Hardware Trojan." 2025 IEEE Computer Society Annual Symposium on VLSI (ISVLSI). Vol. 1. IEEE, 2025

- Darjani, Armin, Nima Kavand, and Akash Kumar. "Flip-UnLock: An Anomaly Detection Attack on Flip-Flop-Based Logic Locking." 2025 IEEE Computer Society Annual Symposium on VLSI (ISVLSI). Vol. 1. IEEE, 2025

- Darjani, Armin, Nima Kavand, and Akash Kumar. "Flip-Break: Breaking Flip-flop-based Logic Locking in Sequential Circuits." Proceedings of the Great Lakes Symposium on VLSI 2025