X-ReAp: Cross(X)-Layer Runtime Reconfigurable Approximate Architecture

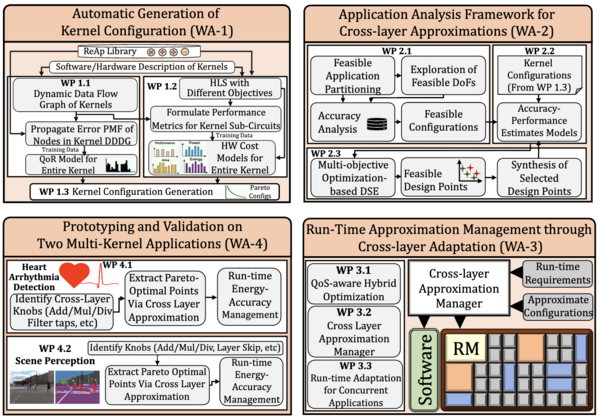

The X-ReAp project extends the achievements of the DFG-funded ReAp initiative, which developed precise and approximate arithmetic modules, quantization techniques for low bit widths, and platform-level support for runtime approximation in hardware accelerators. Building on these foundations, X-ReAp addresses a critical research gap: most existing work isolates approximation to a single abstraction layer, while substantial efficiency gains lie in cross-layer approximation.

The project designs approximate architectures and methodologies that partition applications into subprograms and evaluate approximation strategies across layers using machine learning models. The framework analyzes trade-offs in precision, resource use, and performance (e.g., convolution parameter settings in ML applications), identify admissible accelerator configurations (“operating points”), and dynamically adapt them at runtime to meet evolving application requirements.

The methodology integrates approximate arithmetic libraries and ML-driven impact analysis to support adaptive, energy-efficient, high-performance accelerators. Evaluation targets diverse domains, including image processing, machine learning, healthcare, and audio processing.

Key contributions

Cross-layer approximation methodology and architecture guided by various heuristics and ML models.

Design of heterogeneous approximate hardware configurations.

Runtime accuracy–performance configurability of the proposed architectures.

Validation on different application domains.

Employees Responsible

- Prof. Dr. Akash Kumar

- Dr. Salim Ullah

- Dr. Zahra Ebrahimi

- M. Sc. Yuhao Liu

Selected Publications

- X-DINC: Toward Cross-Layer ApproXimation for the Distributed and In-Network ACceleration of Multi-Kernel Applications

- AxOSpike: Spiking Neural Networks-Driven Approximate Operator Design

- GREEN: An Approximate SIMD/MIMD CGRA for Energy-Efficient Processing at the Edge,

- AxOMaP: Designing FPGA-based Approximate Arithmetic Operators using Mathematical Programming

- AxOCS: Scaling FPGA-Based Approximate Operators Using Configuration Supersampling

- CoOAx: Correlation-aware Synthesis of FPGA-based Approximate Operators

- RAPID: Approximate Pipelined Soft Multipliers and Dividers for High Throughput and Energy Efficiency

- AxOTreeS: A Tree Search Approach to Synthesizing FPGA-based Approximate Operators,

- AppAxO: Designing Application-specific Approximate Operators for FPGA-based Embedded Systems

- Plasticine: A Cross-layer Approximation Methodology for Multi-kernel Applications through Minimally Biased, High-throughput, and Energy-efficient SIMD Soft Multiplier-divider

- BioCare: An Energy-Efficient CGRA for Bio-Signal Processing at the Edg

- CLAppED: A Design Framework for Implementing Cross-Layer Approximation in FPGA-based Embedded Systems

- SIMDive: Approximate SIMD Soft Multiplier-Divider for FPGAs with Tunable Accuracy

- LeAp: Leading-one Detection-based Softcore Approximate Multipliers with Tunable Accuracy