Project description

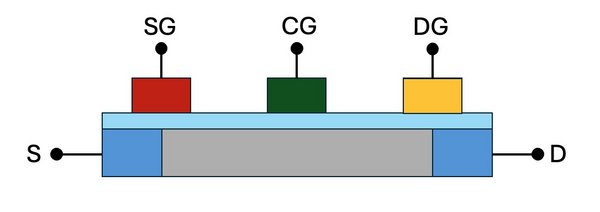

Shrinking feature sizes has long been a major factor to improve CMOS circuit performance. This led to zero-effort performance gains in electronic circuit architecture in the past. By approaching the power wall for current CMOS scaling factors we see an increased need for thermal management and the need to employ dark silicon schemes to provide both the necessary performance and utility at the same time. In this project, we investigate the possibilities for reconfigurable transistors to reshape electronic circuit design to provide a higher functional density while maintaining sufficiently low power consumption. To achieve this, we exploit unique properties like multiple gates per transistor next to their reconfigurability. We focus on a model-based approach to design a new standard cell library by using probabilistic model checking. For this we extend a model checker to design and verify new cells. In close collaboration with nanomaterials research we refine our models to fit the projections and laboratory implementations of emerging technology devices. The new standard cell library will not only map current CMOS cell designs to new technology but will also cover new cells with a higher complexity and thus functionality. We expect that this will put greater load on to the logic synthesis that is responsible for standard cell selection. We also take the logic synthesis flow into account. While an unmodified EDA flow will produce preliminary results, we expect that modifications to technology mapping that take circuit reconfigurability and different cell properties into account will be needed to take full advantage of the new possibilities. Close communication between the model-approach and the EDA flow may also make a logic synthesis approach feasible that circumvents the limitations of current standard-cell-based EDA approaches. We design a comprehensive testing and benchmarking framework. This allows us to not only compare our new design flow against a CMOS EDA flow, but also allows us to track our own progress in standard cell design and modifications to the EDA flow.

Employee responsible

Papers

S Märcker, M Raitza, S Rai, G Galderisi, T Mikolajick, J Trommer, A Kumar, “Formal Analysis of Camouflaged Reconfigurable Circuits”, 21st IEEE Interregional NEWCAS Conference (NEWCAS), 1-5, 2023